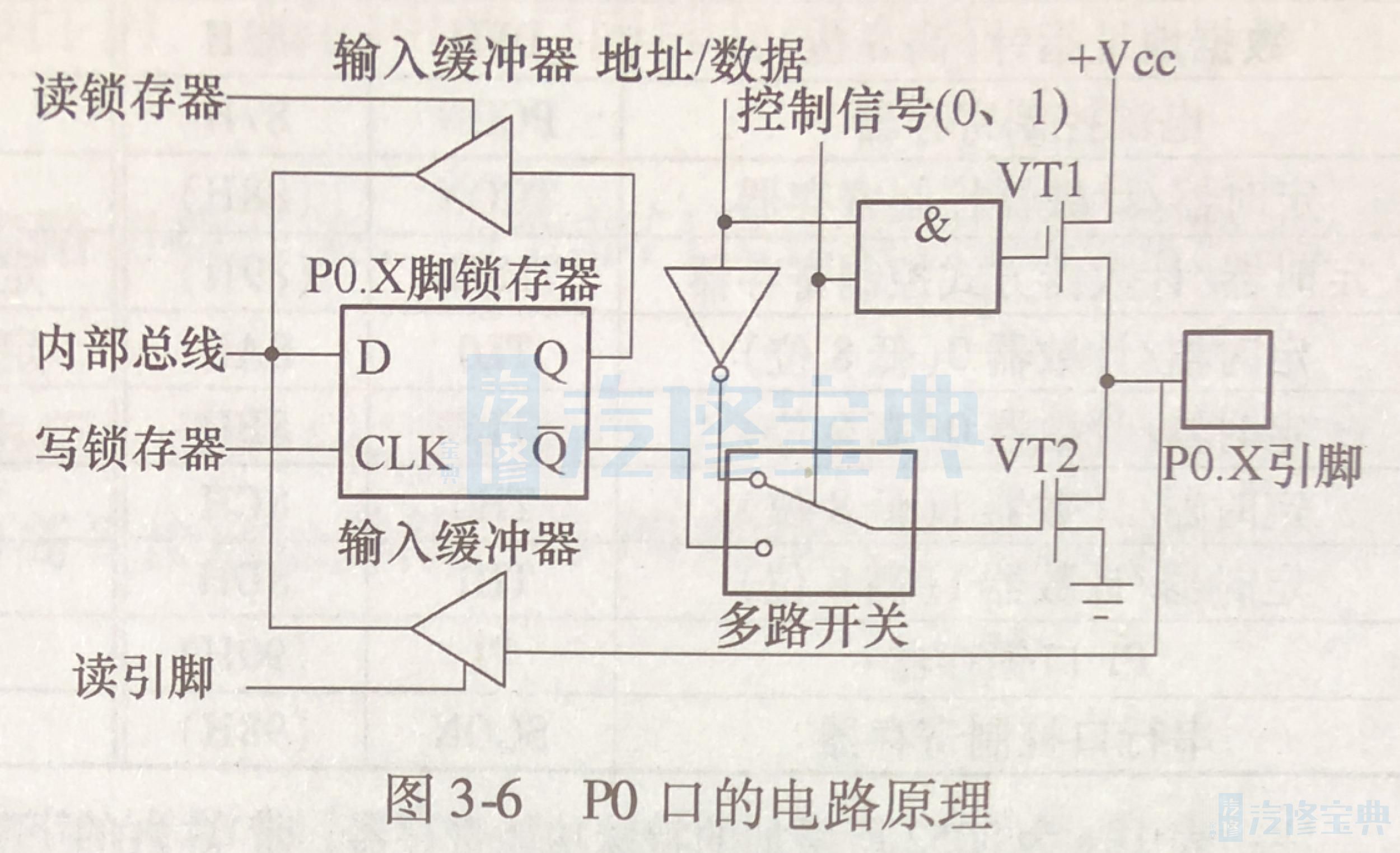

8051单片机有四个8位0端口(P0、P1、P2、P3),连接CPU和外电路,用于信号的输入与输出、地址/数据总线或第二功能。四个I/O端口的功能和结构有所不同,但工作原理有相似之处。 1.P0口的结构与工作原理。 PO端口由锁存器、输入缓冲器、多路切换开关、一个与非门、一个与门及场效应晶体管驱动电路构成,P0端口某一位的电路原理如图3-6所示。

(1)组成部件作用原理。

P0.x锁存器:一位P0.x锁存器由个D触发器构成,当写锁存器端为低电位时(CLK=0),Q、Q端状态不变多路开关:由控制信号控制。控制信号为1时,多路开关与下面接通,P0口作为普通LO口使用;控制信号为0时,多路开关与上面接通,P0口作为“地址/数据”总线使用。

驱动电路:由两个MOS管组成推拉式结构,也就是说,这两个MOS管一次只能导通个。当VT1导通时,VT2就截止;当VT2导通时,VT1截止。

2)P0口用作输入/输出口0口作为LO端口使用时,多路开关的控制信号为0(低电平),多路开关将Q端与VT2的输入端接通。

作为输出口用:CLK=1,Q端连接Ⅴ2输入端。内部总线经锁存器D端、Q端、多路开关、V2与PO端口PO.x脚的引线连接。

作为输入口用:先给锁存器写入1,使Q端置0,使TV2截止;然后将读引脚置1,P0端口P0.x脚的引线与内部总线连接。

读锁存器:当需要读取原输出信号时,读锁存器置1,上输入缓冲器通路,Q端信号输入内部总线(3)P0口用作地址/数据总线P0口作为系统并行口扩展使用时,多路开关的控制信号为1(高电平),多路开关将非门输出端与TV2的输入端接通。

地址/数据总线输出:控制信号=1,与门输出取决于地址/数据总线,地址/数据总线信号通过与门、非门,控制TV1、Tv2通断,使PO.x引脚得到地址/数据总线信号。

数据总线输入:当需要从外部存储器读取数据时,CPU使控制信号置0,并向锁存器置1(Q端置0),V2截止;将读引脚置1,PO端口PO.x脚的引线与内部总线连接。

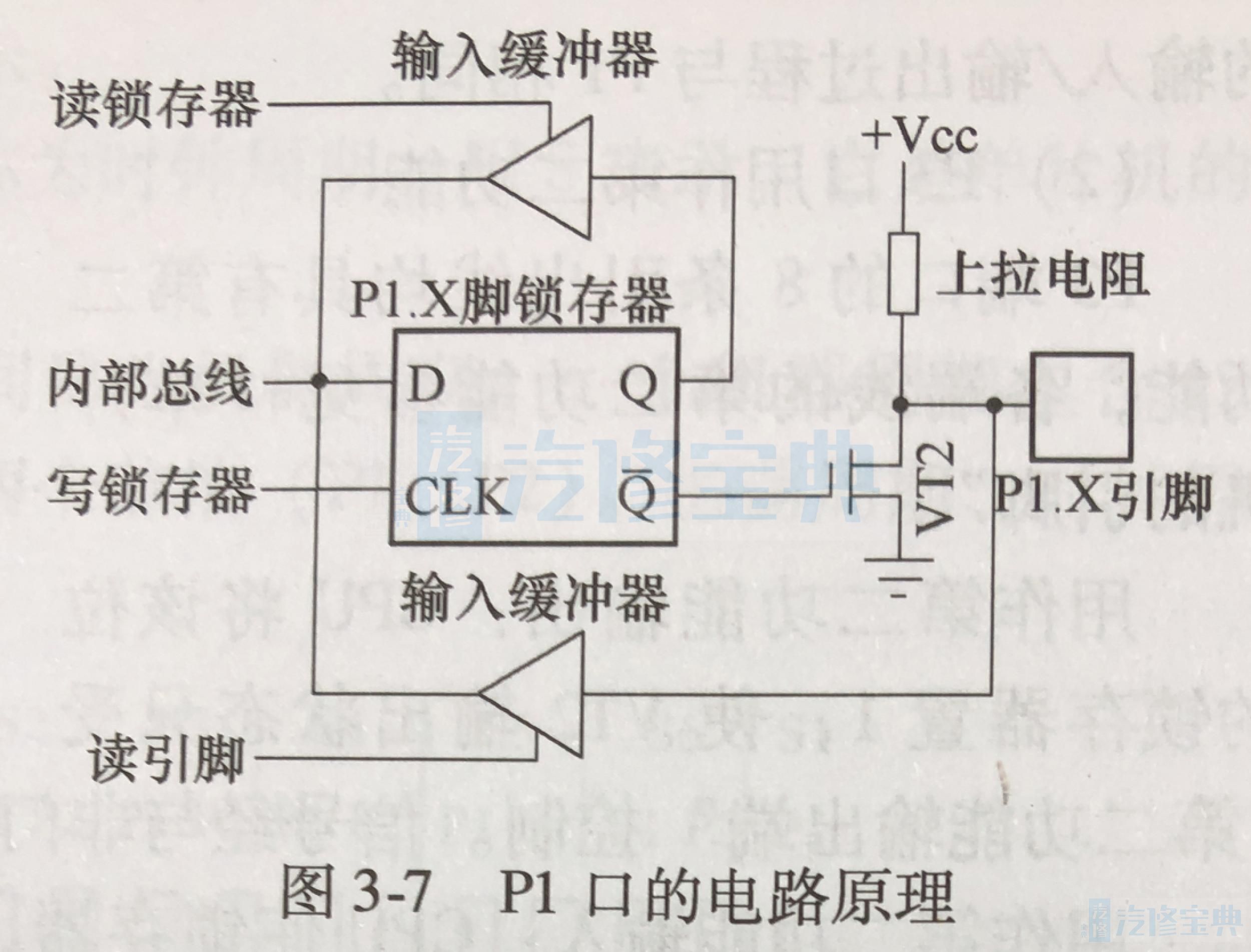

2.P1口的结构与工作原理。

PⅠ端口由锁存器、输入缓冲器及场效应晶体管驱动电路构成,其电路原理如图3-7所与P0相比,P1端口少了与门、非门和多路开关,上拉电阻取代了Ⅵ1,因此,不需要外接上拉电阻。P1的结构形式使它只能作为普通的LO端口。同样,从外读入信号时,需要V2截止,因此,也要先向端口写入“1”。

作为输出口用:CIK=1,Q连接V2输入端。

内部总线经锁存器D端、Q端、VT2与P1端口P1.x脚的引线连接。

作为输入口用:先给锁存器写入1,Q端置0,使VT2截止;然后将读引脚置1,P1端口P1.x脚的引线与内部总线连接。

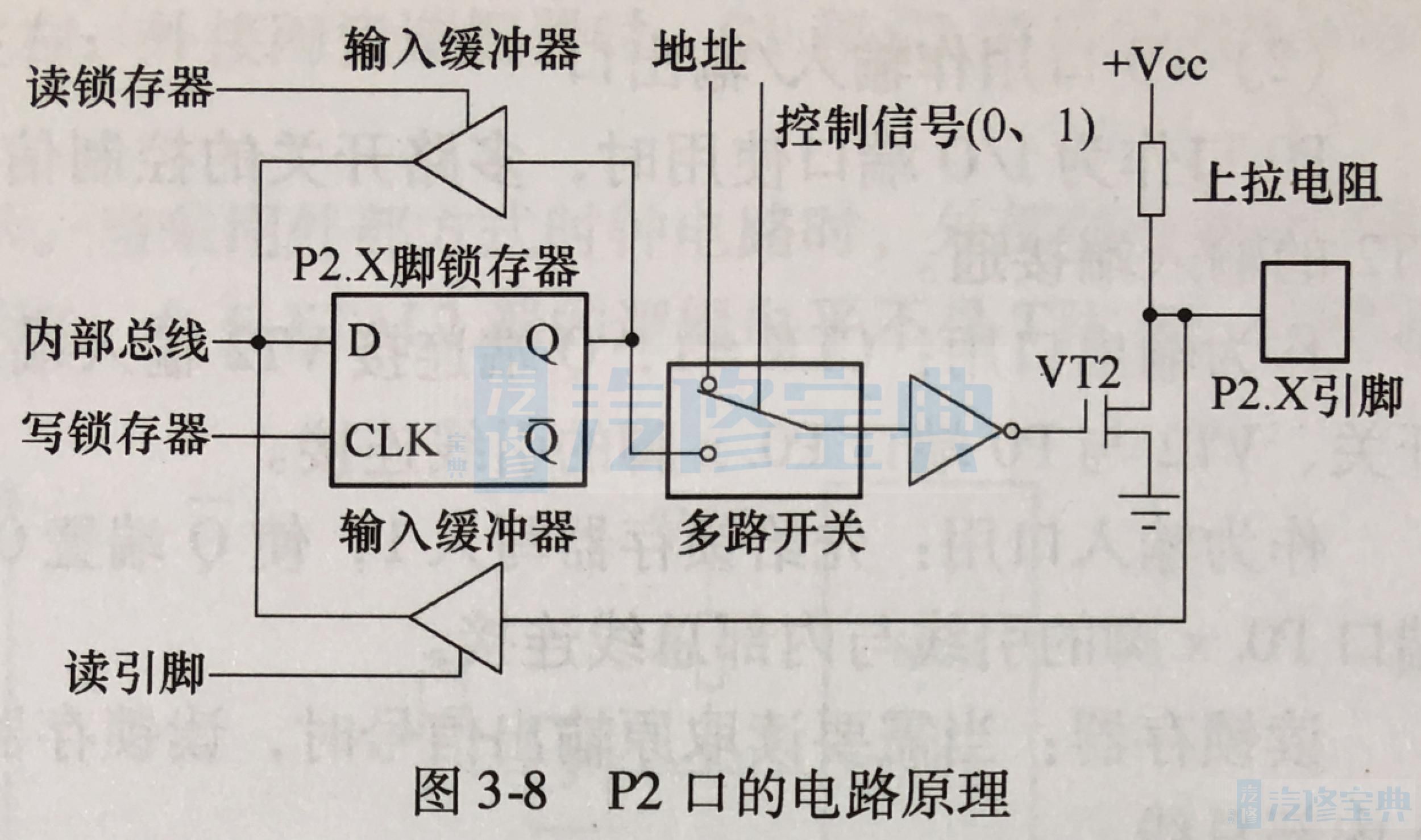

3.P2的结构与工作原理。

P2端口由锁存器、输入缓冲器、多路切换开关、一个非门及场效应晶体管驱动电路构成,其电路原理如图3-8所示。

与PO端口相比,VT1换成了上拉电阻,无与门。P2端口与P0相似,可作为通用的I/O接口使用,也可用作访问外部存储器的高8位地址总线,与P0的低8位一起构成16位地址总线。

(1)P2口用作输入/输出口。

P1口作为O端口使用时,多路开关的控制信号为0(低电平),多路开关将Q端与VT2的输入端接通。

作输出口用:CIK=1,Q端连接ⅥT2输入端。内部总线经锁存器D端、Q端、多路开关、VT2与P2端口P2.x脚的引线连接。

作输入口用:先给锁存器Q端置通过反相器后使VT2截止;然后将读引脚置1,P2端口P2.x脚的引线与内部总线连接。

(2)P2口用作地址总线。

P2口作为高8位地址总线时,多路开关的控制信号为1(高电平),多路开关将地址总线与ⅥT2的输入端接通。

地址总线信号输出:地址总线为1时,通过非门反相后使VT2截止,使P2.x引脚为1;

地址总线为0时,反相后为1,VT2导通,使P2.x引脚为0。

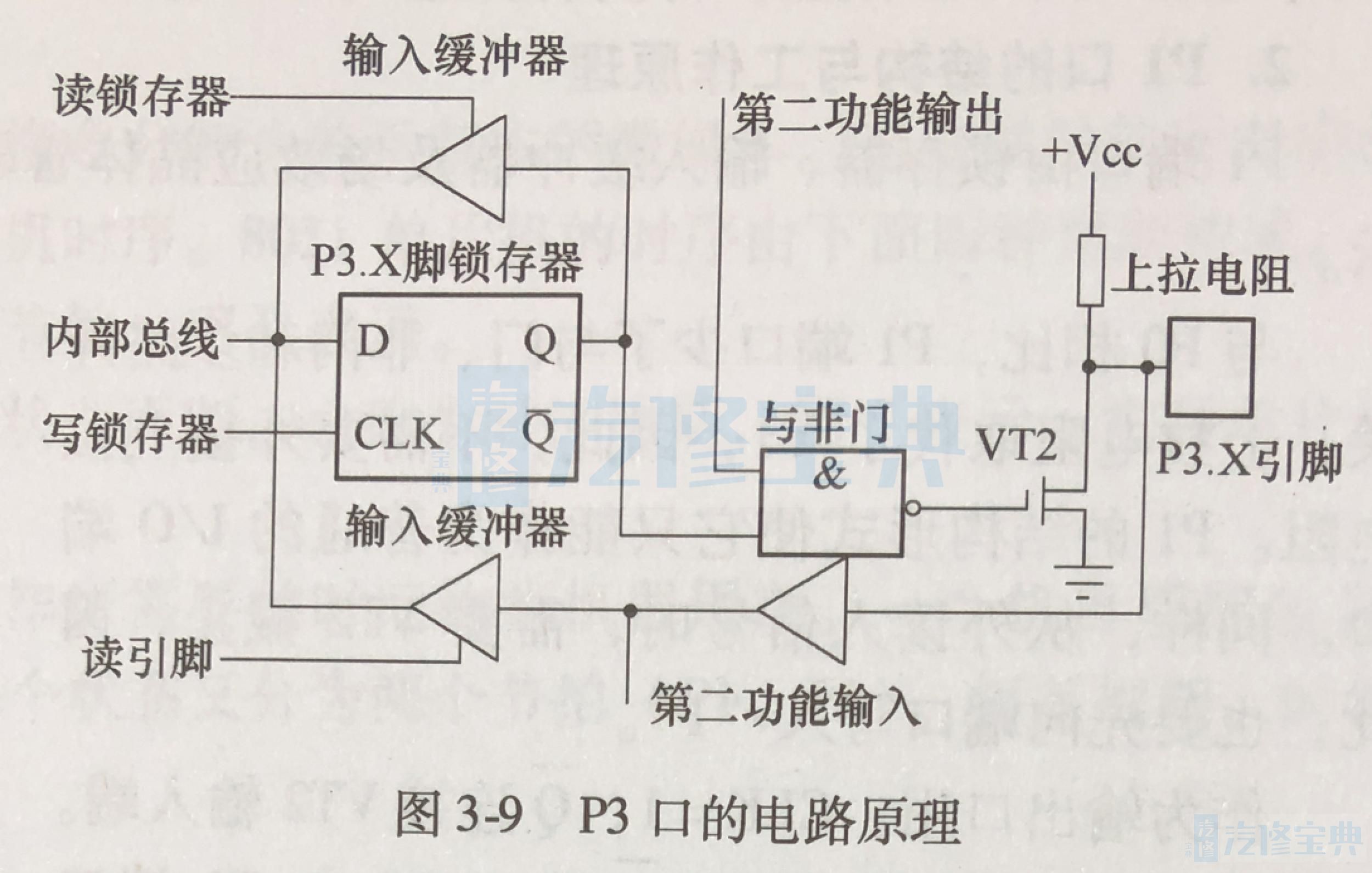

4.P3的结构与工作原理。

P3端口除了可作通用的I/O接口使用外,还具有第二功能。P3端口由锁存器、输入缓冲器、一个与非门及场效应晶体管驱动电路构成,有第二功能输入、输出端,其电路原理如图3-9所示。

(1)P3口用作输人/输出。

P3口作为Ⅳ0端口使用时,第功能输出端置1。此时,内部总线信号的输入/输出过程与P1相同。

(2)P3口用作第二功能。

P3端口的8条引出线均具有第二功能,各端线的第二功能参见“单片机的引脚”。

用作第二功能输出:CPU将该位的锁存器置1,使VT2输出状态只受“第二功能输出端”控制。信号经与非门、VT2两次反相后输出到P3.x引脚。

用作第二功能输入:CPU使锁存器、第二功能输出端置1,使V2截止;P3.x引脚信号经缓冲器3送入第二功能输入端。